Imec përmirëson dritaren e memories së një qelize të kanalit 3D për NAND Flash të gjeneratës së ardhshme

Për disa dekada, NAND Flash ka qenë teknologjia kryesore për aplikacionet e ruajtjes së të dhënave me kosto të ulët dhe me densitet të madh. Kjo memorie jo e paqëndrueshme është e pranishme në të gjitha tregjet kryesore elektronike të përdorimit përfundimtar, të tilla si telefonat inteligjentë, serverët, PC-të, tabletët dhe disqet USB. Në hierarkinë konvencionale të memories kompjuterike, NAND Flash ndodhet më larg nga njësia qendrore e përpunimit (CPU) dhe dihet se është relativisht e lirë, e ngadaltë dhe e dendur në krahasim me memorien statike me akses të rastësishëm (SRAM) dhe RAM dinamike (DRAM).

Suksesi i kësaj teknologjie të ruajtjes lidhet me aftësinë e saj për të shkallëzuar densitetin dhe koston vazhdimisht – shtytësit kryesorë për zhvillimin e teknologjisë NAND Flash. Rreth çdo dy vjet, industria NAND Flash ka përmirësuar ndjeshëm densitetin e ruajtjes së biteve, e shprehur në terma të rritjes së Gbit/mm2.

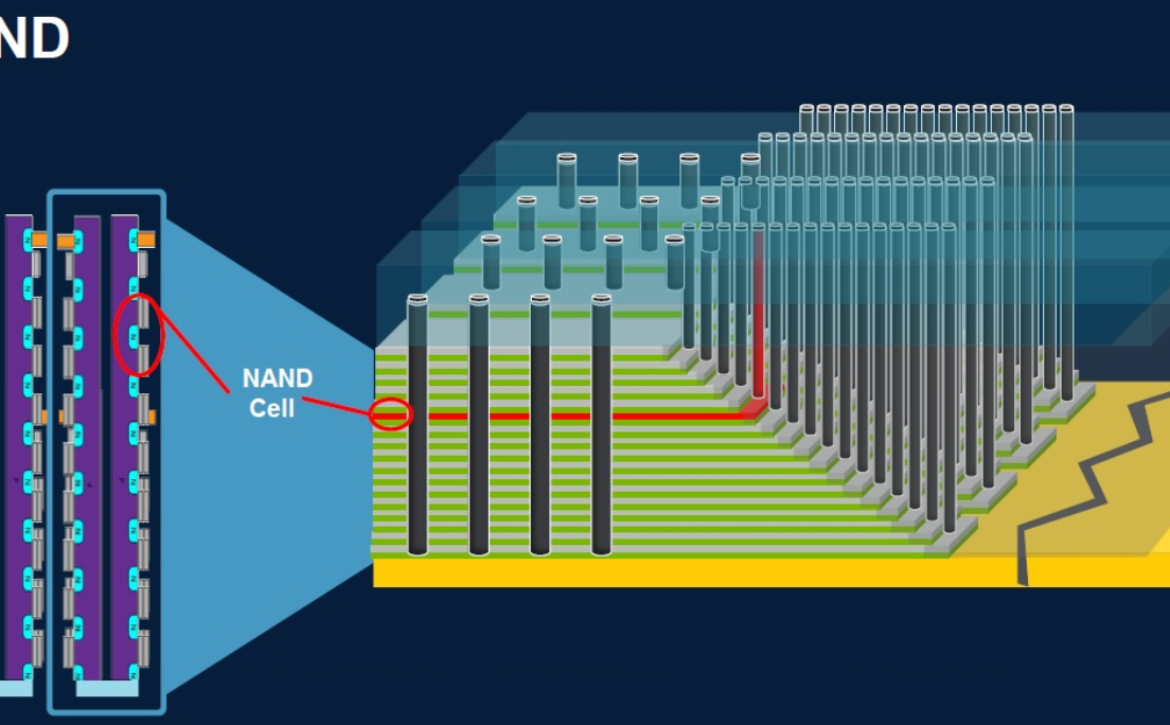

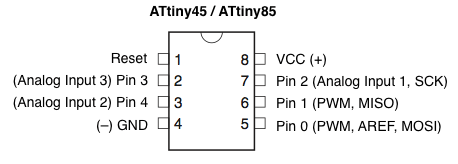

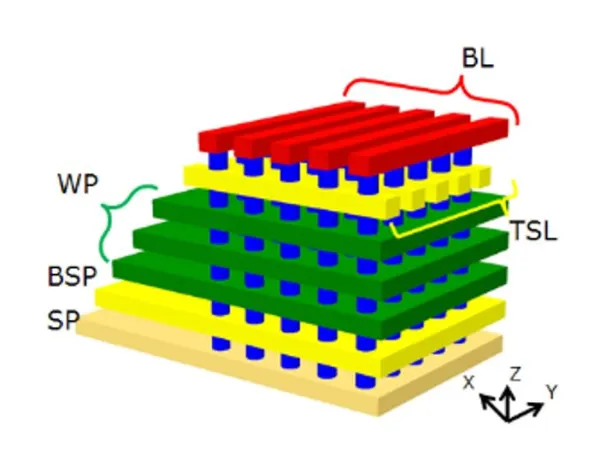

Disa risi teknologjike janë prezantuar përgjatë rrugës për të ruajtur këtë linjë trendi. Kalimi në dimensionin e tretë ishte padyshim risia më mbresëlënëse. Në 3D NAND Flash (Figura 1), qelizat e kujtesës grumbullohen për të formuar një varg vertikal dhe qelizat adresohen me vija horizontale të fjalëve. Risi të tjera të dukshme përfshijnë rritjen e numrit të biteve për qelizë (deri në katër) dhe kalimin nga tranzistori i portës lundruese në qelizën e kurthit të ngarkesës për funksionimin e memories

Më moderne: kanale vertikale me portë; deri në 300 shtresa fjalësh

Megjithëse nuk ndiqet nga të gjithë prodhuesit e memories, qeliza e kurthit të ngarkimit është baza e shumicës së strukturave 3D NAND sot. Kjo qelizë memorie i ngjan një transistori MOSFET me shtimin e një shtrese të vogël nitridi silikoni (SiN) të futur brenda oksidit të portës së tranzitorit (turpi oksid-nitrit-oksid (ONO)). Shtresa SiN përmban shumë vende të bllokimit të ngarkesës që mund të mbajnë një ngarkesë elektrostatike. Kur porta poli-Si anohet pozitivisht, elektronet nga rajoni i kanalit kalojnë tunel përmes shtresës së oksidit dhe bllokohen në shtresën SiN. Kjo rrit tensionin e pragut të transistorit. Gjendja e qelizës mund të matet duke kaluar një tension nëpër nyjet e burimit/kullimit. Nëse rrjedh rryma, qeliza është në një gjendje “pa elektrone të bllokuara” (që korrespondon me 1). Qelizat janë në gjendjen e ‘elektroneve të bllokuara’ (ose 0) nëse nuk matet rryma.

Qeliza e kurthit të ngarkimit dështoi të futej në konfigurimet e mëparshme planare 2D NAND për shkak të një dritareje të pamjaftueshme të memories, e cila matet si diferenca në tensionin e pragut midis programit dhe fshirjes. Por në strukturat 3D NAND, kjo qelizë e njësisë së memories arriti në potencialin e saj të plotë, falë një metode të zbatimit të kanalit vertikal gate-all-around (GAA). Në këtë konfigurim GAA, pirgu i portës mbështillet plotësisht rreth kanalit. Kjo gjeometri cilindrike krijon një efekt të zgjeruar në terren në oksidin e tunelit. Kjo çon në injeksion më të madh të bartësit në shtresat e kapjes, duke përmirësuar dritaren e programit/fshirjes.

Fabrikimi i GAA zakonisht fillon me rritjen e një pirg shtresash oksidi/linjë fjalësh. Më pas, vrimat cilindrike formohen duke shpuar nëpër pirg duke përdorur mjete të avancuara të gravurës së thatë. Shtresat e tunelit (O) dhe të kurthit (SiN) dhe kanali poli-Si më pas depozitohen përgjatë mureve anësore të vrimave.

Kohët e fundit, disa lojtarë të mëdhenj njoftuan prezantimin e produkteve të bazuara në 3D-NAND me deri në 300 shtresa fjalësh të vendosura mbi njëra-tjetrën, dhe ky trend i rritjes së shtresave pritet të vazhdojë edhe në vitet në vijim1.

Mënyrat për të rritur më tej densitetin e ruajtjes së biteve

Gjatë dekadës së tanishme, prodhuesit e kujtesës do ta shtyjnë udhërrëfyesin konvencional GAA NAND në kufijtë e tij përfundimtarë. Pas projeksionit më optimist, numri i shtresave do të jetë rritur në 1000 deri në fund të dekadës, duke llogaritur për densitetin e ruajtjes së biteve 100 Gbit/mm22. Megjithatë, ky është një ngadalësim prej disa vitesh në lidhje me udhërrëfyesin historik të shkallëzimit të densitetit.

Rritja e numrit të shtresave prezanton kompleksitete dhe kosto gjithnjë e më të larta të përpunimit, sfidon proceset e depozitimit dhe etch-it dhe shkakton krijimin e stresit brenda shtresave. Për të kapërcyer këto sfida, industria po prezanton disa ‘mashtrime’ plotësuese të procesit për të marrë përfundimisht 1000 shtresat. Këto përfshijnë ndarjen e numrit të shtresave në dy (ose më shumë) nivele të grumbulluara, rritjen e mëtejshme të numrit të biteve për qelizë, rritjen e efikasitetit të grupit dhe reduktimin e lartësisë x-y të qelizës GAA. Ekziston gjithashtu një prirje për të optimizuar qarkun periferik në një vaferë të ndryshme dhe për ta lidhur atë në grupin e memories duke përdorur teknikat e lidhjes wafer-to-wafer. Megjithatë, këto risi nuk do të jenë të mjaftueshme për të kontrolluar kostot në rritje të përpunimit, dhe për këtë arsye, po ndiqet një shkallëzim shtesë z-pitch. Shkallëzimi me ton Z përfshin një reduktim të lartësisë së të gjitha materialeve të përfshira në grumbullin e shtresave, duke përfshirë metalet dhe oksidet e linjës së fjalës.

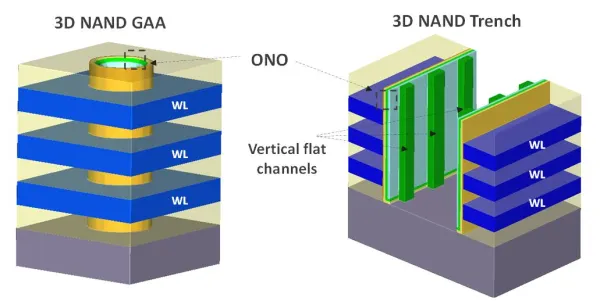

2030: prezantimi i arkitekturës së qelizave të kanalit 3D

Në vitin 2030, pasi shkallëzimi i GAA NAND Flash është ngopur, imec parashikon prezantimin e një arkitekture të re për të lidhur qelizat e kurthit të ngarkesës: arkitekturën e qelizave të kanalit. Me këtë arkitekturë, 3D NAND largohet nga gjeometria rrethore e qelizave të memories GAA. Në vend të kësaj, qelizat vendosen në murin anësor të një kanali – që i ngjan një konfigurimi planar që anohet në anën e tij – me dy transistorë në muret e kundërta të kanalit (Figura 2). Kjo arkitekturë e qelizave NAND Flash të gjeneratës së ardhshme jo vetëm që do të ofrojë hapin e kërkuar në densitetin e ruajtjes së biteve; gjithashtu besohet se zvogëlon kostot. Megjithatë, ashtu si në konfigurimin planar 2D, porta nuk është më e mbështjellë plotësisht rreth kanalit. Prandaj, krijuesit e kujtesës janë të shqetësuar për një dritare të pamjaftueshme programi/fshirjeje.

Programoni dhe fshini sjelljen e kanalit kundrejt arkitekturave të qelizave GAA

Në IEEE 2023 (2023 IMW), imec prezantoi një krahasim eksperimental të funksionimit të memories së një qelize llogore me atë të një qelize memorie GAA3. Të dy variantet e memories NAND Flash u përpunuan në të njëjtën vafer, d.m.th., një mjet testimi 3D NAND i zhvilluar në shtëpi me portë poli-Si dhe tre shtresa të rreshtave të fjalëve. Në vend të vrimave cilindrike, veçoritë e kanalit (300 nm të gjera dhe 1µm të gjata) u gdhendën në pirgun e rrafshit të fjalëve për strukturën e kanalit. Tre kanale vertikale të sheshta poli-Si (me gjerësi kanali 50 nm – 200 nm) janë formuar përgjatë mureve anësore të kanalit dhe janë fabrikuar kryqëzimet e burimit/kullimit.

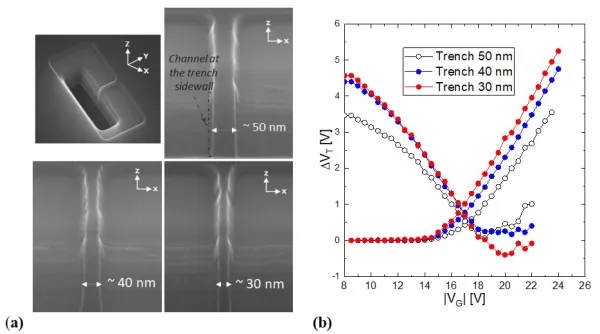

Pa optimizim, qelizat e kanalit nuk funksionojnë aq mirë sa qelizat GAA. Ata kanë efikasitete jo ideale të programit dhe fshirjes, të cilat reflektohen në pjerrësinë dhe fillimin e kurbave të programimit të pulsit të hapave rritës (ISPP) dhe kurbave të fshirjes (ISPE). Kjo përkthehet në një dritare më të vogël programi/fshirjeje. Në anën e fshirjes, kurbat ISPE tregojnë gjithashtu një degradim në nivelin e ngopjes së fshirjes.

Drejt një dritareje memorie 5V

Dritarja e dobët e kujtesës mund të shpjegohet me mungesën e një efekti të fushës të shkaktuar nga lakimi, i cili, në rastin GAA, rrit injektimin e bartësit në shtresën e bllokimit. Për të adresuar këtë mangësi, ekipi i imec doli me një zgjidhje inovative, d.m.th., zvogëlimin e gjerësisë së kanalit të pajisjes së kanalit. Shkallëzimi i gjerësisë së kanalit pritet të zgjerojë ndikimin e rajoneve të lakuar me injeksion të lartë të formuar rreth skajeve të kanalit. Me fjalë të tjera, në një gjerësi kanali shumë të reduktuar, qeliza e kanalit fillon të ngjajë me një qelizë GAA nga pikëpamja gjeometrike.

Nga ana tjetër, degradimi në nivelin e ngopjes së fshirjes përcaktohet kryesisht nga injektimi i elektroneve parazitare nga porta. Kjo mund të shtypet duke inxhinieruar me kujdes pirgun e portës dhe duke integruar një portë metalike.

Imec tregoi eksperimentalisht se një funksionim më i mirë memorie mund të arrihej për pajisjet e kanalit me gjerësi kanali të shkallëzuar (deri në 30 nm), të kombinuara me një material alternativ të linjës së lartë klinike (si ZrO2 ose HfO2 në vend të Al2O3), një oksid tunelimi dhe integrimi i projektuar e një porte metalike (Figura 3). Për shumicën e kushteve të studiuara, u demonstrua një dritare memorie deri në 5V, një përmirësim me 2V – pa ndikuar në mbajtjen dhe sjelljen e çiklizmit. Ekipi aktualisht po punon për përmirësimin e mëtejshëm të programit dhe fshirjen e funksionimit.

Dendësi jashtëzakonisht e lartë e ruajtjes së biteve

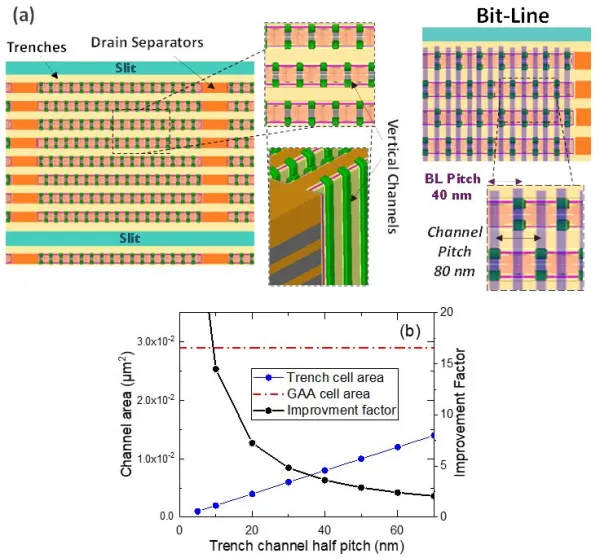

Pasi të keni demonstruar një qelizë të njësisë së memories së kanalit me karakteristika të mira memorie, hapi tjetër është të hetohen skemat e mundshme të integrimit të industrisë për të grumbulluar një numër më të madh shtresash. Një rrjedhë e tillë procesi pritet të ngjajë me një rrjedhë procesi GAA, me shtimin e një moduli shtesë: gdhendjen e shiritave të kanalit të sheshtë vertikal në anën e kanalit. Me kusht që të gjendet një zgjidhje procesi për këtë hap sfidues gravurë, imec propozoi një emulim të një rrjedhe të procesit të kanalit 3D, me llogore me hapje 220 nm, secila llogore është 100 nm e gjerë dhe rreth 1µm e gjatë. Për të siguruar densitet të lartë bit, rrjedha plotësohet duke gdhendur shirita kanali të gjerë 25 nm me një hap 80 nm (Figura 3).

Nga struktura përfundimtare e projektimit, arkitektura e kanalit vlerësohet të ketë një densitet qelizash tre herë më të lartë se referenca GAA. Kjo pritet të përmirësohet më tej me shkallëzimin e zërit të kanalit. Bazuar në këto rezultate, arkitektura e kanalit 3D mund të konsiderohet si një zbulim i mundshëm për memorien e ardhshme 3D NAND Flash, me dendësi të ruajtjes së biteve shumë më tepër se 100 Gb/mm2.

Referenca

https://spectrum.ieee.org/flash-memory

https://semiconductor.samsung.com/newsroom/tech-blog/expanding-storage-solutions-with-nand-flash-technology/